#### **EUROPEAN COMMISSION**

Brussels, 13.12.2018 C(2018) 8864 final

In the published version of this decision, some information has been omitted, pursuant to articles 30 and 31 of Council Regulation (EU) 2015/1589 of 13 July 2015 laying down detailed rules for the application of Article 108 of the Treaty on the Functioning of the European Union, concerning non-disclosure of information covered by professional secrecy. The omissions are shown thus [...]

#### PUBLIC VERSION

This document is made available for information purposes only.

### Subject: State Aid SA.46578 (2018/N) – Germany State Aid SA.46705 (2018/N) – France State Aid SA.46595 (2018/N) – Italy State Aid SA.46590 (2018/N) - United Kingdom

## **Important Project of Common European Interest (IPCEI) Microelectronics**

Sirs,

#### 1. **PROCEDURE**

(1) On 10 October 2016, Germany and the United Kingdom ("UK"), followed by Italy on 11 October 2016 and by France on 12 October 2016, pre-notified the above mentioned measures concerning an important project of common

| Seiner Exzellenz Herrn Heiko MAAS<br>Bundesminister des Auswärtigen                                                                   | Onorevole Enzo Moavero Milanesi<br>Ministro degli Affari esteri e della                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Werderscher Markt 1                                                                                                                   | Cooperazione Internazionale                                                                                                                                     |

| D - 10117 Berlin                                                                                                                      | P.le della Farnesina 1                                                                                                                                          |

|                                                                                                                                       | I - 00194 Roma                                                                                                                                                  |

| Son Excellence Monsieur Jean-Yves Le Drian<br>Ministre de l'Europe et des Affaires étrangères<br>37, Quai d'Orsay<br>F - 75351- PARIS | The Rt Hon Jeremy HUNT<br>Secretary of State for Foreign Affairs<br>Foreign and Commonwealth Office<br>King Charles Street<br>London SW1A 2AH<br>United Kingdom |

European interest ("IPCEI") in the fields of microelectronics<sup>1</sup> on the basis of a common draft overall descriptive text (so-called "Chapeau" document), to be thereafter complemented with the detailed information on the project and its components as and when progress would be made in the discussions between Member States and companies on the set up of the project.

- (2) The Commission requested complementary information by letters dated 18 November 2016 and 22 March 2017, to which the Member States replied by letters dated 13 January and 19 May 2017. Further information was requested on 12 July 2017. Meetings were held between the Commission services and the pre-notifying Member States on 12 October 2016 and 16 February 2017.

- (3) On 4 January 2017, the German authorities informed the Commission of their intention to allow enterprises to start their works on the project after having submitted a complete aid application. No public funding was granted yet as it is subject to a formal approval by the Commission

- (4) On 8 September 2017, the German authorities submitted a brief overview of the German companies intended to participate in the IPCEI Microelectronics project and an intended State aid amount. In November 2017, discussions started on the template documents to be submitted for each company participating to the IPCEI Microelectronics and on the documents describing the underlying projects.

- (5) On 20 December 2017, the German authorities committed to the German aid beneficiaries<sup>2</sup> to award aid under the condition of approval of the aid by the Commission.

- (6) In December 2017, the Commission services took the initiative to organise high level meetings and working group meetings at technical level in order to enhance coordination between Member States and ensure progress in the delivery of information on the underlying projects in the prenotification stage.

- High level meetings took place on 17 January 2018, 22 March 2018, 8 June 2018, and 18 September 2018. Meetings at technical level took place on 24 January 2018, 6 March 2018, 22 March 2018 and 10 April 2018.

- (8) As of the end of May 2018, the German authorities started providing first drafts of the documents describing the German companies' activities in the IPCEI Microelectronics. End of June 2018, the UK authorities provided first drafts of the documents describing the UK companies' activities in the IPCEI Microelectronics. End of July 2018, the Italian authorities submitted the documents for the Italian companies. At the beginning of July 2018, the French authorities started submitting the documents for the French companies. The Commission assessed the information in detail, in particular the eligibility and

<sup>&</sup>lt;sup>1</sup> Microelectronics relates to the study and manufacture of very small electronic designs and components at micrometre-scale or smaller. These devices are made from semiconductor materials, and in particular the vast majority is made out of silicon.

$<sup>^{2}</sup>$  [...] (\*).

<sup>\*</sup>Confidential information

compatibility of the IPCEI Microelectronics, the necessity of the aid, the research, development and innovation ("R&D&I") content of the research and development ("R&D") projects, R&D&I content of the first industrial deployment (also "FID") projects, end of the FID, eligible costs and funding gaps, spillovers and distortions of competition. To this end, the Commission assessed the submitted documents and requested further information in order to be able to carry out its assessment. The Member States complemented the information throughout August to November 2018.

- (9) Germany, France, Italy, and the United Kingdom (hereinafter also collectively "the Member States") notified the abovementioned measures, respectively on 29 November (Italy) and 30 November (Germany, France and the UK) 2018. Further clarifications were requested by the Commission on 6 December 2018 and the German, French, Italian and UK authorities replied to such request on 6, 7 and 10 December 2018.

- (10) By letters of 24 September 2018, the German and Italian authorities, and, by letter of 11 October 2018, the French authorities, respectively, agreed to waive their rights deriving from Article 342 of the Treaty on the Functioning of the European Union ("TFEU") in conjunction with Article 3 of Regulation No 1<sup>3</sup> and to have this Decision adopted and notified in English.

## 2. **DESCRIPTION OF THE MEASURES**

#### 2.1. Objectives of the measures

#### 2.1.1. Objectives of the IPCEI Microelectronics measures

- (11) The Member States intend to grant aid to upstream microelectronic component manufacturers to carry out research, develop innovative technologies and carry out first industrial deployment in the EU, in order to enable research and development (R&D) on downstream microelectronics applications in two main markets, namely Automotive and Internet of Things<sup>4</sup> ("IoT"), as well as other important markets for Europe like space, avionics, and security.

- (12) The Member States submit that the Important Project of Common European Interest on microelectronics "Connecting Europe's microelectronic industry to foster digitisation in Europe" <sup>5</sup> aims to develop a component offer that covers the full range of functionalities. The majority of electronic products must embed at least 3 or 4 different types of substrates, processes or components to gain their full functionality / autonomy / performances / cost affordability and create the systems required by markets.

<sup>&</sup>lt;sup>3</sup> Council Regulation No 1 determining the languages to be used by the European Economic Community (OJ 17, 6.10.1958, p. 385).

<sup>&</sup>lt;sup>4</sup> The Internet of Things (IoT) is the network of devices, vehicles, and home appliances that contain electronics, software, actuators, and connectivity which allows these things to connect, interact and exchange data.

<sup>&</sup>lt;sup>5</sup> Hereinafter referred to as "the IPCEI", or "the IPCEI Microelectronics".

(13) The overall objective of the IPCEI Microelectronics project is to develop innovative microelectronics technology and components<sup>6</sup> for Automotive, IoT and other key applications and to establish first industrial deployment in these fields, in order to unlock the full technological and economic potential of the Key Enabling Technology ("KET") microelectronics and to transfer it to downstream industries for new or improved applications as well as new R&D in these sectors.

### 2.1.2. Contribution of the IPCEI Microelectronics to European Union's objectives

- (14) The Member States submit that the IPCEI Microelectronics aims at contributing to the KETs<sup>7</sup> strategy and the microelectronics strategy<sup>8</sup>, 'Europe 2020'<sup>9</sup>, the 'Industrial policy'<sup>10</sup>, and will enable value creation in downstream industries.

- (15) Microelectronics has been identified by the Commission as one of the six KETs, crucial for the future development of European industry. As such, they are a priority for European industrial policy. The European Strategy for KETs aims to increase the exploitation of KETs in the EU and to stimulate growth and to create jobs. In its document "Europe 2020 strategy for smart, sustainable and inclusive growth"<sup>11</sup>, the European Commission proposes a response to "Europe's innovation gap": "To boost future productivity and growth, it is critically important to generate breakthrough technologies and to translate them into innovations (new products, processes and services) that are taken up by the wider economy."

- (16) In the Member States' view, the IPCEI Microelectronics directly supports these goals by providing the building blocks for new products and services which will become available and affordable for the population at large as the digitalization of society. Especially electronic components and systems contribute to the development of disruptive technologies across sectors, such as automotive and mobility (e.g. autonomous driving), energy (e.g. electricity management), and healthcare (e.g. remote monitoring). By enabling innovative solutions for societal needs and in the process of creating pan-European ecosystems along the value and supply chains, electronic components and systems are driving answers to respond to Europe's grand challenges.

- (17) In addition, the purpose of the IPCEI Microelectronics is to foster cooperation in the large European ICT sector and especially across diverse IoT market segments. For this reason, the Member States consider that the proposed IPCEI is aligned with "Europe 2020"<sup>12</sup>, the European Union's ten-year jobs and growth

<sup>11</sup> COM(2010) 2020 final, 3.3.2010.

<sup>&</sup>lt;sup>6</sup> The specific details are described in sections 2.2. and 2.6. below

<sup>&</sup>lt;sup>7</sup> 'A European strategy for Key Enabling Technologies — A bridge to growth and jobs', COM(2012) 341 final, 26.6.2012.

<sup>&</sup>lt;sup>8</sup> 'A European Strategy for micro- and nanoelectronic components and systems', COM(2013) 298 final, 23.05.2013.

<sup>&</sup>lt;sup>9</sup> 'Europe 2020, A strategy for smart, sustainable and inclusive growth', COM(2010) 2020 final, 3.3.2010.

<sup>&</sup>lt;sup>10</sup> 'An Integrated Industrial Policy for the Globalisation Era — Putting Competitiveness and Sustainability as the Centre Stage', COM(2010) 614 final, 28.10.2012.

<sup>&</sup>lt;sup>12</sup> COM(2010) 2020 final, 3.3.2010.

strategy, and Horizon 2020, "the main instrument for implementing Innovation Union, one of the most crucial initiatives of the Europe 2020 growth strategy."

(18) Microelectronics generates directly and indirectly employment all along the strategic European value chains, creating growth and wealth in the whole EU's economy. The Member States refer to the Commission Communication on the strategy for micro- and nanoelectronic components and systems.

## 2.1.3. Examples of downstream applications involved

- (19) Further, the Member States point out some of the contributions of microelectronics on downstream applications:

- Microelectronics industry is a key contributor to EU's technology nondependence in strategic domains with a clear reference to the emerging security issues. The European microelectronics industry allows to produce advanced critical devices to serve strategic sectors like transport, energy, health, finance, defence and space that have become increasingly dependent on network and information systems to run their core businesses. Europe has a need for a wide range of concrete measures that will further strengthen the EU's security capabilities in the microelectronics field, as a leverage effect to ensure that the EU is better prepared to face the ever-increasing security challenges.

- Europe's ability to innovate and improve its technology portfolio in all key industrial sectors depends on its ability to integrate high performance, low power and low cost semiconductor solutions in every single designed and manufactured product. For instance, with the onset of the automotive and IoT<sup>13</sup> networked economies, the need for a stable supply of trusted semiconductors is increasing even further. As the next wave of digitization is coming, existing European downstream value chains (automotive, industrial, aerospace, logistics, energy, lighting as a few examples) need to explore the opportunities which will be enabled by advances in microelectronics. This is also a chance to create new value chains in the EU.

- In the near future in the automotive application domain, autonomous driving cars will require several components deriving from the IPCEI Microelectronics program and able to address two main challenges for the innovative cars: security and connectivity. The ultimate goal for a fully autonomous vehicle would be to dramatically cut the accidents rate, thanks to the electronics and software it will utilize. This will mainly happen due to large capacity of computation in real time, high speed/low consumption silicon chips but also dozens of cameras, detecting devices (radars, sensors, ...) to locate the car in its environment and alert on potential risks, and RF (radio frequency) components for the interaction of the car with other cars, the road infrastructure and various dedicated networks. The development of electric vehicles focuses on batteries, but also on the power semiconductor chips that will allow controlling the electricity flow between batteries and electrical motors on board.

- In addition, 5G, or the fifth generation of cellular technology, is characterized by its heightened speed, responsiveness and ability to handle

<sup>&</sup>lt;sup>13</sup> For all acronyms, please see Annex 1.

a huge amount of connected devices. 5G could serve as the communications foundation for emerging technologies like autonomous driving, thus handling very sensitive data. Europe has to maintain its know-how for this potentially sensitive technology. As the risk of cyber-physical attacks is increasing, European industry as well as European citizens should be able to rely on the fact that neither their data nor the control of cars and machines can be improperly manipulated. Therefore, it has to be ensured that the microchips (and systems) cannot be influenced by external sources and that they offer enough security against all kinds of cyber-attacks, guaranteeing highest security and safety standards. The full control of this is only possible if security and safety are already built in into the chip design and are based on common understanding and standardisation. This requirement applies to all microelectronic components used in these emerging technologies.

(20) The Member States submit that the semiconductors are the components that are capable of producing such strong spillover effects, as the chips are an enabling key factor to provide technical solutions that address societal challenges or at least provide real-life applications for the users. The functionality of every single electronic device can be traced back to hardware (usually in conjunction with software). The versatility of microelectronics components makes this technology indispensable for every downstream market and across all industrial sectors.

#### 2.2. Description of the IPCEI Microelectronics

- (21) This section describes the IPCEI Microelectronics as it has been presented by the Member States in the notification.

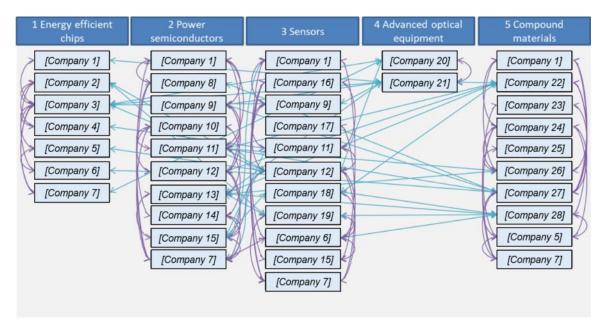

- (22) The IPCEI Microelectronics is organised along five technology fields (TFs):

- TF1: Energy efficient chips;

- TF2: Power semiconductors;

- TF3: Sensors;

- TF4: Advanced optical equipment; and

- TF5: Compound materials.

Within each of these fields, the participating undertakings will conduct both R&D&I and first industrial deployment (FID) activities.

- (23) According to the Member States, FID in this IPCEI will allow for the development of new products with high research and innovation content and/or for the deployment of fundamentally innovative production processes. The success of the FID of a new technology and its related products will require a high level of integrated R&D&I on a continuous basis. The R&D&I efforts of industrial partners (within the FID phase) in collaboration with Research Organisations ("ROs") to achieve the FID will concern *inter alia*:

- the development of specific tools or methodologies,

- the collaboration within the whole European microelectronics ecosystem,

- the development of new technologies in close collaboration with dedicated suppliers (substrate, equipment, raw materials...),

- the development of platforms and open-access technologies.

- (24) This IPCEI also comprises R&D works, focusing on:

- the development of new technologies for the next generation of devices, such as more energy efficient chips (along the More-Moore paradigm<sup>14</sup>), more powerful power devices, smarter sensors and faster bit rate communications,

- the adding of new functionalities to current devices (More-than-Moore paradigm<sup>15</sup>),

- the adaptation of current technologies to cope with emerging applications,

- the development of next generation products.

- (25) These R&D works will result from close collaborations between the industrial partners, ROs and academic laboratories that are (or will be) involved in the IPCEI Microelectronics, as well as end-users.

- (26) Such R&D works could also involve academic and industrial partners, which are not part of this IPCEI and which do not belong to any member state of this IPCEI, through European projects in the frame of the Eureka PENTA cluster or of the JU ECSEL. These collaborations will ensure the efficient dissemination of the results obtained within this IPCEI through the whole microelectronics ecosystem.

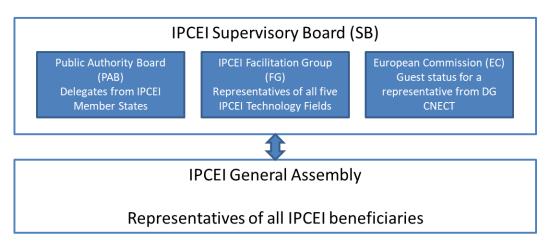

- (27) Within each TF, a number of partners (participating companies) will join their efforts to address important challenges in the relevant field. The work in each TF will be organised in a number of work packages. The figure below summarizes the industrial partners and research organisations involved in each technology field of the IPCEI Microelectronics.

<sup>&</sup>lt;sup>14</sup> "More-Moore" corresponds to the miniaturization of the digital functions leading to electronic components benefiting from exponentially increasing computational power from one generation to the next.

<sup>&</sup>lt;sup>15</sup> "More-than-Moore" refers to functional diversification of semiconductor-based devices. It complements digital signal and data processing in a product. These functions may imply among others analogue and mixed signal processing, the incorporation of passive components, high-voltage components, microsystems, sensors and actuators. "More-than-Moore" technologies allow non-digital functionalities to migrate from the system board-level into the package or onto the semiconductor chip. Technological progress from one technology generation to the other is not based on pure downscaling of structure widths on the semiconductor chip, but on optimizing a variety of parameters on the semiconductor chip as well as of the package design.

| Project management              |                           |                             |                                 |                                       |  |

|---------------------------------|---------------------------|-----------------------------|---------------------------------|---------------------------------------|--|

| 1 Energy efficient<br>chips     | 2 Power<br>semiconductors | 3 Sensors                   | 4 Advanced optical<br>equipment | 5 Compound<br>materials               |  |

| CEA-Leti                        | 3-D Micromac              | CEA-Leti                    | AMTC                            | AZUR Space Solar                      |  |

| Cologne Chip                    | AP&S International        | CorTec 🗧                    | Carl Zeiss*                     | Power                                 |  |

| Globalfoundries                 | CEA-Leti                  | Elmos                       |                                 | CEA-Leti                              |  |

| RacylCs                         | Elmos                     | Semiconductors              |                                 | Integrated Compound<br>Semiconductors |  |

| Soitec*                         | Semiconductors            | Fondazione Bruno<br>Kessler |                                 | IQE*                                  |  |

| ST Micro-                       | Infineon*                 |                             |                                 | Newport Wafer Fab                     |  |

| electronics                     | MURATA                    |                             |                                 | SPTS Technologies                     |  |

| X-FAB                           | Robert Bosch              | Robert Bosch*               |                                 |                                       |  |

|                                 |                           | ST Micro-<br>electronics    |                                 | OSRAM                                 |  |

| * Coordinator                   | ST Micro-                 |                             |                                 | Sofradir                              |  |

|                                 |                           | TDK-Micronas                |                                 | Soitec                                |  |

|                                 | X-FAB                     | ULIS                        |                                 | ST Micro-                             |  |

| Name in <i>"italic"</i> = SME   |                           | X-FAB                       |                                 | electronics                           |  |

| Dissemination and communication |                           |                             |                                 |                                       |  |

Figure 1: overall structure of the IPCEI Microelectronics

- 2.2.1. Energy efficient chips (Technology Field 1, TF1)

- In TF1, eight partners<sup>16</sup> in Europe will work to jointly address the challenge of (28)improving the energy efficiency of basic microelectronic components, or chips. The participating entities aim to focused and aligned R&D&I for a qualitatively new class of products - energy efficient chips. The involved companies will continue by transferring these learnings into an FID phase. This, in turn, is expected to allow European companies to accelerate their R&D&I efforts leading to several significant benefits: the European R&D&I ecosystem along the entire value chain (upstream and downstream) to be strengthened, and innovative products and applications to be developed faster As a consequence, such strengthened European value chains are expected also much better to address a second big area of concern - the security at the chip or hardware level. The purpose of TF1, in order to contribute to the objectives of the IPCEI Microelectronics will be to develop, including in the FID, new, relevant, innovative, and energy-efficient techniques which will lead to new components to be incorporated in innovative end-products and applications in order to reverse the trend of ever higher power consumption by ICT/IoT in the future. So FID itself will lead to further R&D&I efforts in the TF1 community.

- (29) The member states affirm that the participants in TF1 are jointly executing an important element of the European KET strategy in the field of Micro- and Nanoelectronics. Their focus is on advancing the energy efficiency of chips, a real challenge in light of the unprecedented proliferation of wired and wireless electronic devices connected with each other via the Internet. This challenge cannot be addressed by one entity alone regardless of its expertise in micro- and nanoelectronics. It takes close cooperation along the entire supply chain towards

<sup>&</sup>lt;sup>16</sup> Considering separately ST – France and ST – Italy

the common objective of increasing the energy efficiency of microelectronic components, or chips.

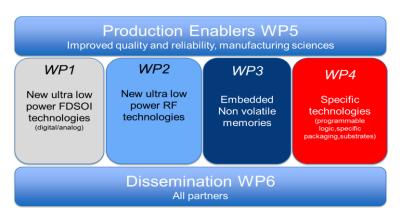

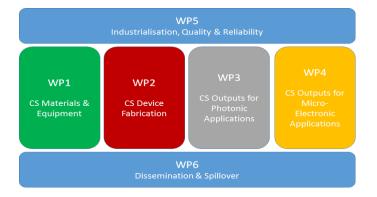

(30) In order to facilitate and structure the cooperation within TF1, the work will be broken down into six major technical work packages ("WP"). Four of them are dedicated to technology development in line with the targeted application domains. Before first industrial deployment can occur, additional R&D activities have to be carried out such as meeting quality and reliability requirements as well as assuring manufacturability. These aspects are addressed in WP5. Another important aspect of the IPCEI Microelectronics is dissemination and spillover, and a specific WP6 is addressing that in order to maximize the impact of this project.

Figure 2: work packages in TF1

WP1 - New ultralow power FDSOI<sup>17</sup> technologies. This part covers the (31) FDSOI technology at the 28nm, 22nm and subsequent 12nm node. This energyefficient technology is key in applications such as autonomous driving, computing, industrial, IoT, and aerospace, where computation capacity is required with a low power footprint. These technologies provide answers to the challenges brought by the various applications. In this domain, one of the objectives is to facilitate the FDSOI uptake by European industry in order to strengthen the upstream eco-system's innovation potential. Another objective to further close the gap between the digital and analogue realms. If signal or data processing is more and more digital, the interface with the real world is still analogue. As a consequence, there is a lot of demand for very efficient analogue technologies either as a dedicated one or as add-ons to the digital technologies in order to improve their performance in the analogue/mixed signal domain. The challenge is to develop highly performant European technologies which enable applications offering a real differentiation and combining the best from both digital and analogue domains.

<sup>&</sup>lt;sup>17</sup> Silicon on insulator (SOI) technology refers to the use of a layered silicon-insulator-silicon substrate in place of conventional bulk silicon substrates in semiconductor manufacturing. In Fully Depleted Silicon On Insulator (FDSOI) devices, the silicon surface layer is very thin so that the electrically-induced switching of electrons supports less interference resulting in higher switching speeds.

- (32) WP2 New ultra-low power Radio Frequency (RF<sup>18</sup>) technologies. The need for wireless communications is unlimited as it goes beyond connecting humans to connecting objects. It puts high pressure on RF technologies to keep up the pace of innovation. Switches, low-noise and power amplifiers, require improved figure of merit, that is, improved performance and/or efficiency of an innovative chip to address the new challenges posed by car-to-car and car-to-infrastructure communication, by proliferation of very low power communicating IoT devices, by e.g. low bandwidth IoT networks, and by 5G. The objective is to preserve the European position in communication by providing system makers with the best technologies to answer their new challenges in a most innovative and energy-efficient manner.

- (33) WP3 Embedded non-volatile memory. This is a very important technology especially for applications facing a very constrained energy budget such as IoT nodes. In this case, the major objective is to provide performant technologies which are able to support operations in a low power environment such as automotive or devices which need to function without batteries. This WP is targeting the development of various innovative flavours of embedded memories such as PCRAM, MRAM, and other R&D&I to FID activities.

- (34) **WP4 Specific technologies.** [...] One of the main objectives of WP4 is to provide tailored European technology solutions for fields such as IoT, Artificial Intelligence or space applications. The value stems from a strong and well-defined interaction between advanced wafer substrates, new chip designs and innovative semiconductor process technologies. [...].

With the slowdown of Moore's Law<sup>19</sup>, the need for more integration of different functionalities on one chip and even more innovative packaging of one or more chips in one encasement is coming. This is driven by very specific conditions (such as in space) and by the need of integration of heterogeneous functions (such as digital, RF, and antennas). This WP is able to leverage the knowledge and technology present in Europe in order to provide new and innovative solutions for downstream users.

- (35) **WP5 Moving to FID.** This WP will address all the activities needed in a FID phase. To move an innovative technology from the stage of R&D&I to the subsequent FID stage requires a great deal of learning and continuous improvement efforts in terms of quality, reliability and manufacturability. Many sectors like medtech, automotive, security and aerospace for example have very stringent requirements on all of those dimensions. The required targets can only be met in a carefully planned and executed FID process.

- (36) **WP6 Dissemination.** Efforts will be undertaken to make the achievements of WP1 through WP5 available to a broad community of stakeholders including end users, large OEMs, SMEs and start-ups as well as ROs and academia.

<sup>&</sup>lt;sup>18</sup> RF technologies are the different technologies involved in wireless communications, among others WiFi, mobile voice and data communications. They cover the wide radiofrequency spectrum from 3Hz to 3THz and the wide variety of technologies to generate and detect radiowaves.

<sup>&</sup>lt;sup>19</sup> The exponential growth in computing power predicted by Moore's Law, named after Intel co-founder Gordon Moore, enables on a two-year cycle chips that are consistently more powerful than their predecessors even as the cost of that computing power falls.

Depending on the type of results, publications, technical events or commercially available IP will create an outreach far beyond the direct and extensive indirect scope of the IPCEI Microelectronics.

(37) The participating partners in TF1 will be Soitec, Globalfoundries, ST, X-Fab, Cologne Chip, Racyics and CEA-LETI.

The participating companies in this TF1 and their specific contribution will be the following:

- (a) SOITEC (WP 1, 2, 4, 5 and 6): The FDSOI engineered substrates are the key to allow FDSOI technologies achieving industrial targets. The goal of the material specialist Soitec is to develop SOI substrates with high uniformity and low defect density and sufficient to enable foundries to ramp-up 28 nm, 22 nm, and 12 nm FDSOI technology node. The FDSOI innovation roadmap will be addressed in RD&I activity: it is aimed to provide SOI substrates with thinner buried oxide layers, so that the substrate will be the requirements of 12 nm technology node. Furthermore, new functionalities /.../ will be added to current FDSOI substrate in order to increase their RF performance [...]. The targeted RF-SOI engineered substrates in 300 mm wafer diameter will bring cost and power effective approaches. Therefore, Soitec aims to develop 300 mm RF-SOI substrates which go well beyond the current state-ofthe-art of 200 mm wafers. The RF-SOI innovation roadmap will also be addressed in R&D&I with the purpose to demonstrate RF-SOI engineered substrates with new materials enabling increased linearity performance and stability [...]. In addition, new Piezo-On-Insulator (POI) wafers [...] will be developed in the project. [...]. These activities of the partner Soitec will take place in new "Fab5G" line, Bernin 2 extension and Bernin 3.

- (b) Globalfoundries' (WP 1, 2, 3, 4, 5 and 6) goal in this project is the further development and establishment of the promising FDSOI technology. Therefore, the 22 nm technology node will be advanced in R&D&I activities and transferred to FID. In the FID phase, activities will be manifold process alignment and extended methods for process stability as well as the design for manufacturing and testing. It is aimed to enhance the diversity of FDSOI technology by using its outstanding properties (e.g. back-biasing) and thus, to develop a benchmark of new technology variants applicable for RF, mmWave and eNVM devices. With these devices, Globalfoundries targets to meet recent and future applications in IoT, consumer, and automotive. [...]. Finally, specific reliability for automotive applications will be demonstrated.

- (c) ST (WP 1, 2, 3, 4, 5 and 6): The goal of ST is the development of a new generation of 28 nm FDSOI technology targeting low operating voltage for high-end and energy efficient microcontrollers. It is aimed to improve the RF capabilities of this technology as well as its robustness against harsh environments (e. g. in space applications). This also includes the introduction of dedicated FDSOI devices for high level hardware security in current and future nodes but also new packaging technology. Furthermore, it is aimed to research on high reliability and cost efficient process technologies based on Partial Depleted Silicon-on-Insulator

(PDSOI) to meet the requirements of low-power RF applications. In this context, ST will develop and evaluate novel dense eNVM cells in 40 nm technology node and novel Phase Change Materials in 28 nm technology node for their applicability in new non-volatile concepts. The overall target is to provide ultra-low power secure microcontrollers for automotive applications.

In particular, ST-France will be involved in developing and deploying ultra-low power FDSOI and RFSOI technologies, as well as new embedded non-volatile memories for MCU. Within this project some of its tasks will also concern the design of advanced devices based on these technologies.

ST- Italy will design and develop next generations of digital integrated circuits for microprocessors and ASICs, with specific critical safety functions like ADAS (Advanced Driver Assistance System) or autonomous driving and navigation.

Thus, planned RDI activities will cover the future devices for ADAS, 32bit MCU (Micro-Controller Unit), and Telematics.

- (d) X-FAB (WP 2, 4, 5 and 6) offers foundry services for processing analogue and mixed-signal semiconductor applications. In this project, X-FAB will develop chip level heterogeneous integration of different materials to improve the transmission and RF performance as well as functional reliability of novel energy efficient chips. In this context, enhanced SOI substrate materials offering high impedance will be developed. [...]. Furthermore, X-Fab will develop Process Design Kits with different level of maturity to demonstrate its technology to industrial partners.

- (e) Racyics (WP 1, 2, 4 and 6) as an expert of designing analog, mixedsignal and digital integrated circuits (IC), targets on developing a versatile and energy efficient Multi-Processor System-on-Chip (MPSoC) platform for IoT applications. [...]. Furthermore, it is aimed to evolve IC design standards which meet the possibilities of the 22 nm FDSOI technology provided by Globalfoundries [...].

- (f) Cologne Chip (WP 1, 2, 4 and 6) as a developer and manufacturer of application-specific integrated circuit (ASIC) aims to develop and characterize novel structures and technologies for Field Programmable Gate Array (FPGA) applicable in 28 nm, 22 nm, and 12 nm FDSOI technologies. In this context, extensive investigations on timing and power extraction as well as modelling for integrated circuits required for industrial partners will be performed.

- (g) CEA-LETI (WP 1, 2, 3, 4 and 6) aims to conduct fine analysis and develop an understanding of critical physical parameters and processing steps in order to develop future SOI substrates for the FDSOI technology. This includes the advancement of next structure generations of 12 nm and sub-12 nm width in close cooperation with Soitec. Furthermore, in cooperation with the partner ST, CEA-LETI targets on the further diversification of 28 nm FDSOI technology node. In this context, novel

RF devices and functions based on this technology node as well as embedded Non-Volatile-Memories (eNVM) based on Phase Change Materials (PCM) are developed to be applicable in automotive and IoT. For completing the research portfolio, CEA-LETI will advance metal oxide based resistive Non-Volatile Memories (OxRAM), Magnetoresistive Random Access Memories (MRAM) as well as novel memory effect materials (e.g. Ferroelectric RAM) as potential alternatives. As a last goal, CEA-LETI will address silicon-based devices for quantum computing, neuromorphic architecture, and 3-dimenional monolithic integration to be able to offer technologies for future applications and the on-going digitalization.

- (38) TF1 is necessary for the overall objective of the IPCEI Microelectronics because the urgency of improved energy efficiency and radiofrequency connectivity is cutting across all technology fields and downstream ICT markets and applications. The progress within TF1 will greatly contribute to the overall success of this IPCEI.

- (39) According to the Member States, without the public funding provided within the frame of the IPCEI Microelectronics, R&D&I as well as R&D in FID efforts undertaken by the involved TF partners in the field of energy efficient and secure chips would be significantly lower in the European Union. This would deny the partners the opportunity to fully exploit the benefits of a technology whose time has come as application domains like IoT, Automotive, and Medtech etc. posing new challenges in terms of power foot-print and security. Eventually, the advances made possible by TF1, that is, the highly expected reduction of the carbon footprint from advanced electronic systems would not occur to the same extent. Specifically, without the aid to TF1, the consequences at technological level would be that the FDSOI and RF-SOI technology would not be further developed and the benefits in terms of energy efficiency and forthcoming 5G standards and components in Europe would not materialize. The partners in TF1 would resort to older, mature technologies. That would have a strong negative impact on the overall success chances of the IPCEI Microelectronics and its relevance for downstream markets like IoT which require more energy efficient solutions like the ones aimed at with the work within TF1.

- 2.2.2. Power semiconductors (Technology Field 2, TF2)

- (40) In TF2, eleven partners<sup>20</sup> in Europe will cooperate to jointly address the challenge of power semiconductor devices with increased energy efficiency and reliability. Chip and package more and more merge and often chip and packages are only successful as a combined device where the chip and package are tailored to each other. The introduction of Industry  $4.0^{21}$  capabilities in the fabrication processes of these devices [...] will lead to more stable processes and thus improve reliability and robustness of the final semiconductor device. Robust devices have a higher durability, which reduces the electronic waste. The

<sup>&</sup>lt;sup>20</sup> Considering ST – France and ST – Italy separately

<sup>&</sup>lt;sup>21</sup> Industry 4.0 refers to the fourth industrial revolution corresponding to the current trend of automation and data exchange in manufacturing technologies. All objects (things) embark computing and sensing capacity are become connected in network to realise a truly intelligent system.

combination of power semiconductor devices with hardware based encryption (in a package or on a board) will enable critical infrastructures to be resilient against cyber-attacks.

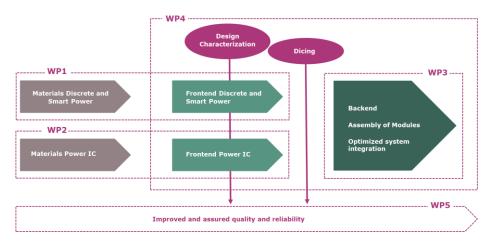

- (41) The goal of TF2 is to strengthen the European R&D&I in power semiconductors and integrated smart power solutions along the relevant value chain (chip technologies, assembly techniques, design/libraries, digital manufacturing, quality/reliability). The improvements along the value chain are a precondition for power semiconductors and integrated smart power circuitries of smaller size with less energy losses, with smaller cooling structures, with longer lifetime and meeting advanced application and market requirements.

- (42) The respective contributions of the power semiconductor industry can be summarized in four major technical objectives:

- Sustainable energy generation and conversion,

- Reducing energy consumption,

- High reliability and functional safety enabled by embedded on-chip diagnostics,

- (43) Efficient community energy management. According to the Member States, in order to structure the work within TF2, this technology field is organised in 5 work packages:

Figure 3: work packages in TF2

(44) WP1 – New smart power and power discrete technologies, with alternative materials (like GaN or SiC) as well as innovative combinations of different technologies, are mastering the more demanding market applications. Smart power technology integrates in the same chip different circuits having technological solution fulfilling different functions (analogue, logic and power). Such diversification allows approaching a wide range of application from automotive, industrial, healthcare, consumer, robotics, with the upmost goal to improve electronic systems efficiency and finally global CO<sub>2</sub> reduction. In addition, specific technological solutions allow improvement in terms of power density management simplifying package design and finally the product reliability. WP1 covers all essential aspects for the technology development (cost-efficiency, standards, test, etc.); including a variety of smart power process options and the critical process steps devoted to power discrete devices development. The variety of technology options will allow pushing forward the

new devices' innovation and differentiation. The WP1 goal is to push forward innovation in technologies, processes, and demonstrators and enhance the functionalities and performances of smart power devices according to the BCD technology roadmap (Bipolar CMOS DMOS (Double-Diffused Metal-Oxide-Semiconductor)) as well as of discrete power devices. The activities will be finalized to develop and validate new smart power devices and key process modules for discrete power devices on advanced technology platforms that will include smart power process technology node, featuring state of the art Power devices, high-density logic CMOS devices, high performance analogue devices and dense NVM architecture. Process development will be supported by advanced simulations for an effective design and by the processing of technology ramp up and monitor vehicles for reliability qualification and monitoring. The new technology platforms based on new alternative compound materials with SiC and GaN processes, will be the technological pillars featuring state of the art power devices, to address high performance devices with new architectures, and innovative modules for both diodes and discrete power devices.

- (45) WP2 New High Voltage (HV) technologies for power integrated circuits driving to better energy saving and efficiency improvement for automotive and industrial applications. Development of integrated power solutions for motor control and functional safe DC/DC applications using mixed technologies as the evolution of the smart power technologies from devices integrating a few power elements to a huge numbers of HV ([...]) drivers for medical or imaging applications. [...]. HV application are present not only in industrial and lighting market, but also in Automotive, where batteries pack involve some hundreds volts and galvanic solution represents the best approach. [...].

- (46) **WP3 New assembly techniques** are related to the so called backend process of encasing dies (chips) in materials such as plastic, ceramics or metal. The objectives are to:

- Prevent the physical damage and corrosion of the semiconductor device,

- Support the electrical contacts to connect the smaller and thinner chips of the future to a circuit board,

- Dissipate heat produced in the device.

The work carried out under IPCEI Microelectronics includes development of new innovative package solutions with focus to enhance system integration. [...].

(47) **WP4** – The focus of WP4 will be on development and implementation of **concepts according to Industry 4.0** to optimize the trade-off between flexibility and efficiency for the technologies worked out in WP1&2 (frontend related) and WP3 (assembly and packaging related). New automation concepts based on Industry 4.0 will ultimately lead to better quality of the devices made in Europe. For assembly and packaging, which supports system integration by multi-chip packaging, the work on Industry 4.0 (e.g. towards automation) is new in contrast to frontend technology. Thus, R&D&I in WP4 will strongly support the FID of the frontend related work in WP1 & 2 and the assembly and packaging related work in WP3.

# (48) **Supporting WP5 – Improved and assured quality and reliability** during the implementation of new technologies.

The required specifications are measured at different stages of the fabrication process of semiconductor devices:

- Wafer test metrology equipment is used to verify that the wafers have not been damaged by the various processing steps up until testing,

- Once the front-end process has been completed, the semiconductor devices are subject to a variety of electrical tests to verify they function properly,

- The packaged chips are retested to ensure that they were not damaged during packaging and that the die-to-pin interconnect operation was performed correctly.

These are the first level reliability tests, i.e. tests that investigate just the packaged device. Thermal cycling and high temperature storage are examples of such tests. Moreover, second level reliability tests are required, which cover the application board, typically a printed circuit board. [...].

- (49) The contribution of the participating companies in this field will be:

- (a) 3D-MICROMAC (WP 1, 2, 3, 4 and 5) will provide a new dicing technology which can be used for all types of wafers. More specifically, the work comprises of further development of TLS-Dicing<sup>TM</sup>-technology and adoption to a broad range of power semiconductor products. Further development of microDICE<sup>TM</sup> machine technique with regard to requirements of the project partners as well as of additional potential European customers. 3D-Micromac will provide the technology to partners in form of a job shop model to support the development of new semiconductor products. Furthermore, 3D-Micromac will provide the technology in form of the "Pay-per-cut" model to selected partners at their own production site.

- (b) AP&S INTERNATIONAL (WP 4) is a provider of equipment used for wafer wet-chemistry based processing technologies. The scope of work are development up to FID encompasses: the development of tools for wet-processes performed on wafers up to 300mm diameter and thinned to 40µm thickness substrates with highly-controlled process window options; the solutions developed use advanced robotics and new software features tailored to the scope of automation. Milestones have been defined for individual development packages used to develop, test and sample parts used by AP&S for the overall system design of the equipment.

- (c) CEA-LETI will closely collaborate with Murata and ST in this project [...]. In this context, CEA-LETI and Murata aim to develop innovative dielectrics, new electrodes and associated process steps for advanced capacitors and show their performance in a technology demonstrator. Furthermore, CEA-LETI will conduct R&D&I activities on gallium nitride (GaN) power electronics and targets to meet the requirements giving by the partner ST.[...].

- (d) ELMOS SEMICONDUCTOR's work (WP 2, 4 and 5) aims to R&D new HV technologies, developing manufacturing concepts up to FID to meet

high process quality and reliability. R&D&I will be carried out on the development of integrated power solutions for Motor Control and functional safe DC/DC applications using mixed technologies including assembly and packaging solutions, the development of corresponding strategies and solutions for failure analysis, reliability and test. Frontend-related work: HV mixed-signal CMOS technology; Backend-related work: R&D&I and FID for high parallel mixed-signal functional electrical test for power applications.

- (e) INFINEON TECHNOLOGIES (WP 1. 2. 3. 4 and 5) aims to conduct research and development concerning both, frontend and backend-related technologies. This includes the frontend-related work of technology development of RF for power applications based on GaN (gallium nitrate). Backend-related work will relate to packaging of power devices [...].

- (f) MURATA (WP 1 and 4) is contributing innovative technologies for advanced passive components. This work addresses new smart power and power discrete technologies and developing and testing new concepts for manufacturing up to FID. Its frontend-related work will comprise of development of new advanced passive technology in order to be used in several applications compatible with the systems and technology (GaN, Si, etc.) developed by the IPCEI partners (incl. signal and power processing caps (high density, high breakdown voltage) and hybrid caps for energy management [...]. The company will also perform FID wafer fab line for innovative advanced passive technology.

- (g) BOSCH (WP 1, 2, 4 and 5) aims to develop new techniques, which, thus, concern frontend-related work. This includes:

- Developing novel power technologies: Smart power in mixed signal technologies and high power discrete technologies with an emphasis on automotive applications will be advanced. [...]. These developments will be accompanied by the introduction of a series of innovations on the 3D integration and assembly, wafer thinning and high voltage isolation.

- Increasing substrate diameter: Parts of the R&D activities are carried out in the existing 150 mm and 200 mm process lines. The remaining R&D and FID activities will take place in a new 300 mm facility to be built.

- (h) SEMIKRON (WP 1, 2, 3, 4 and 5) will perform mostly backend-related work: development of innovative processes for sinter interconnect and assembly with highest reliability and performance in power modules, the study of device reliability and ruggedness, the development of innovative fast test methods as well as the assembly of clean room power modules and systems with highest automation and quality standards; and cleanroom power module and system assembly line with highest automation and quality standards.

- (i) ST Microelectronics France (WP 1, 2, 3, 4 and 5).

Frontend-related work:

- Power GaN device developments and First Industrial Deployment for power application

- [...]

- Advanced Silicon device developments and First Industrial Deployment for power and IoT applications

Backend-related work:

- Package solution developments and First Industrial Deployment for GaN device integrations for power application and space

- [...]

(j) ST Microelectronics Italy (WP 1, 2, 3, 4 and 5).

- Frontend-related work:

- Power technologies (smart power technologies with differentiation in BCD (Bipolar CMOS DMOS) technology and power discrete technologies: [...]

- Production line ramp-up of "More than Moore" disruptive power technologies and first production parameters optimization

Backend-related work:

- New process technologies for System in Package mastering the big challenges in the packaging area

- X-FAB Germany (WP 1, 2, 4 and 5) aims to develop new techniques, (k) which concern frontend-related work. This includes: development and FID of integrated High Voltage devices up to 700 V for modular integration in CMOS-based technologies and their demonstration in automotive, industrial and medical applications; R&D&I on GaN-on-Si technology modules in a CMOS-process environment. Furthermore, R&D&I activities on quality and reliability will be conducted: characterisation and modelling for robust and reliable power technologies including tests during FID; yield analysis and improvement for complex integrated smart power technologies; implementation of advanced process monitoring and advanced process control methodologies. During FID phase, X-FAB targets to develop new and advanced manufacturing concepts. In this context, real-time fab intelligence processes and other innovative fab logistic solutions for existing and new semiconductor processes and equipment will be developed and implemented. It is aimed to enable highly flexible manufacturing of small and medium production volumes up to FID of these techniques.

- (50) According to the Member States, without the public funding provided within the frame of the IPCEI Microelectronics, R&D&I as well as R&D in FID efforts by the relevant industry in the field of power semiconductors would be significantly lower in the European Union and technological innovation as well as novel contributions to the value chain would not develop in the EU. The directly involved partners would not invest without the funding. This would lead to lower technological competences; the technological solutions on device security will not be developed to their full extent. The reduction of the carbon footprint from advanced systems would not take place to the same extent. Further progress in e-mobility would be delayed.

### 2.2.3. Smart sensors (Technology Field 3, TF3)

- (51) The Member States submit that TF3 aims at enabling European sensor industry to develop and provide sensor components to the European market and thereby improving cooperation and R&D with respect to the European sensor industry. The twelve partners<sup>22</sup> of the TF3 cover the relevant value chain in Europe: sensors are at the core of most advances in the field of automotive electronics, IoT, including home and factory automation as well as health and well-being, authentication systems e.g. for security purposes, smart farming and efficient networks (communication, power, utilities) management in Europe. Smart sensors are also critical components in strategic segments such as aeronautics and space, which makes them a strategic asset.

- (52) Sensors are the eyes and ears allowing controlling critical systems. They comprise optical, acoustic but also mechanical, magnetic, chemical, electrical and other types of sensors. They transform physical, real life information into a signal that can be used by electronic systems. Making sensors smarter is a necessity to reliably gather the right parameters resulting in processed and compressed data, which constitute the relevant information to be transmitted. Without mastering the right sensors and their integration the systems cannot become smart themselves. This is why the base elements developed in TF3 are becoming pervasive and are used in more and more applications.

- (53) The Member States also point that another important aspect is to develop components for secure and trusted recording, transformation, transmission and processing of information. Complex systems with distributed intelligence, e.g. required for autonomous driving functions, need a comprehensive security architecture in order to prevent security violations. Smart sensors of the future will have increased signal classification and processing capabilities and consequently are the first line of defence against hacker attacks and security threats.

- (54) Member States ascertain that would TF3 not be successful, the overall fields of security (biometric authentication is one example), industry and farming automation, automated driving as well as smart health care technologies would risk safety and security problems, delays and loss of relevance, or worse an uncertainty in the supply of critical components.

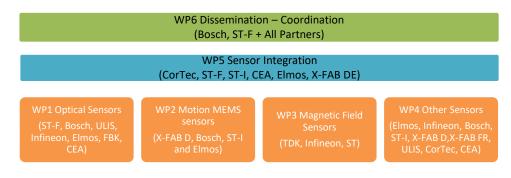

- (55) The Member States submit that innovative sensors will be developed for various purposes by the partners of the IPCEI Microelectronics project towards first industrial deployment. The devices will achieve the full range of sensory functions to cover for the needs of Europe. The work in TF3 will be organised along the following work packages:

<sup>&</sup>lt;sup>22</sup> Considering ST – France, ST – Italy, X-Fab France and X- Fab Germany separately

Figure 4: work packages in TF3

- (56) **WP1 Optical Sensors** (ST, Bosch, ULIS, Infineon, Elmos, FBK). A first important ability will be to perform object recognition by optical or alternate means the eyes of a technical system. Optical sensors include image but also ranging sensors, ALS (ambient light sensors) and UV-index sensors, among others. *[...]*. Such different technologies permit to address the demanding needs of Automotive (Security, ADAS) and other growing sectors in Europe (Industry 4.0, Smart Cities, Wellness, AR).

- (57) WP2 Motion MEMS sensors (X-FAB DE, Bosch, ST-I, Elmos). Motion MEMS sensors such as accelerometers and gyroscopes had the largest share of all MEMS produced since they are used in automotive (airbag, ESP...) and consumer electronics (switch portrait/landscape, gaming). They will continue to deliver an important contribution in the future as well. Therefore, several partners prepare first industrial deployment for sensors with novel approaches and applications. WP2 will work on a new technology for MEMS sensors improving sensitivity, resolution, bandwidth, and form factor to enable their usage for new application. *[...]*.

- (58) **WP3 Magnetic Field Sensors** (TDK, Infineon, ST, Elmos). Owing to their various advantages like contactless sensing and high reliability, Hall sensors are indispensable components in the automotive and industrial sector. [...]. The next generation of sensors will outperform their predecessors' in different generic terms like sensitivity or signal to noise ratio, but also in further relevant characteristics like robustness and reliability (e.g. by stress-compensation or prevention technologies). Connectivity and smartness of such systems are also features, which are required by the "outer world" in which these sensors will be embedded and operated.

- (59) WP4 Other sensors (Elmos, Infineon, Bosch, ST-I, X-FAB DE, X-FAB FR, ULIS, CEA LETI, CorTec). In addition to optical and motion sensors, the expected sensory functions will leverage on / will be completed by the use of other physical sensors. They are piezoelectric, thermal, acoustic magnetic, or electrical sensors as an example, as well as temperature sensors and touch sensors, and more. In the framework of the IPCEI Microelectronics project, key involved project owners will aim to develop the next generation of these kinds of sensors for the targeted applications as automotive, IoT, health and others. [...].

- (60) **WP5 Sensor Integration** (CorTec, ST, CEA-LETI, Elmos, X FAB DE). All the different sensor types need to be integrated into a system in order to develop their full potential. This sensor integration is of crucial importance for the

performance of the final sensor system. The IPCEI partners within the TF3 will work on this sensor integration by preparing different technical solutions, which will provide several options to users and partners downstream the value chain for their specific final automotive or IoT systems. New System-in-Package solutions as well as new heterogeneous integration technologies to combine chips of different materials like micro-transfer printing will be investigated and developed in the TF3. Furthermore, the development and implementation of connection technologies like Through-Silicon-Vias to provide vertical electrical conductive connection through the silicon wafer are key to achieve at the end a 3D integration of different semiconductor components like MEMS sensors with CMOS integrated circuits with minimized footprint and height as required for mobile application for example. Novel soft (with silicone rubber) and hard (with ceramics) encapsulation technologies with high channel feed-throughs will be explored for providing sensors and systems for harsh environments.

- (61) **WP6 Coordination and Dissemination (all partners).** This work package contains the activities between partners involving cooperation within the technology field, participation to the overall governance of the IPCEI Microelectronics, and dissemination activities.

- (62) The contribution of the individual partners in TF3 to the IPCEI Microelectronics project are the following:

- (a) CEA-LETI (WP 1, 4, 5 and 6): together with ULIS, CEA LETI will work on a set of innovative technologies for Long Wavelength IR (LWIR) thermal sensors (so-called microbolometer). The aim is to establish brandnew thermal-based perception systems to Mobility (mainly Automotive) and Society (IoT) applications will work on enabling technologies and design for innovative CIS and Time-of-Flight devices, including pixel design, process steps, optics, 3D technologies, IPs and circuit design. In this context, the RO will closely work with ST as an RO, CEA LETI is only performing R&D&I activities (and as such no FID).

- CorTec (WP 4, 5 and 6) will establish a new cleanroom facility with (b) dedicated and customized micro-machining equipment and for R&D, usability complementary laboratories and reliability investigations and testing to be able to develop innovative implantable MEMS-based sensor arrays and systems to enable electrical interaction with neural tissue for novel biomedical applications. CorTec's biomedical systems will use new chip technologies developed by other partners within IPCEI Microelectronics. Beyond the health applications, additional uses of the developed technologies will be explored in collaboration with the partners in this IPCEI Microelectronics (in all TFs) and with already established and new collaborations with European players outside of this IPCEI.

- (c) Elmos (WP 1, 2, 4 and 6) aims to develop innovative mixed-signal (acoustic, optic, electromagnetic, thermal, pressure) sensor system solutions required for applications such as electric mobility, autonomous driving, smart home, smart car, medical applications, Industry 4.0 and security and start first industrial deployment. Additional R&D&I is planned along the sensor developments for needed functional testing, reliability and quality as well as assembly and packaging. Along with the

new sensor applications, strategic investments are necessary in sensor labs for R&D as well as sample and product verification, in new equipment for sensor processing and flexible test platforms allowing high parallel mixedsignal functional test. The further expansion of cleanroom capacities from previously unused space (in the Elmos fab in Dortmund) for laboratories and testing is planned.

- (d) FBK (WP 1 and 6) will contribute to develop innovative Silicon Photomultipliers (SiPM) and Single Photon Avalanche Diodes (SPAD) with 3D integration. It will execute development and first industrial deployment of these optical sensors applicable for Automotive, health and IoT, and will enable technologies for 3D Integration and open platforms (PdK) for MPW (Multi-Project-Wafers). Therefor, FBK will develop novel technologies (e.g. Through Silicon Vias (TSV), Hybrid Bonding) for processing the envisaged high sensitive image sensors (SiPM and SPAD). It is aimed to integrate these technologies into a CMOS-like process and to provide 3-dimensional (3D) heterogeneous integration with deepsubmicron CMOS readout electronics. The development of a reliable and reproducible process of TSV-SiPM will complete the project.

- (e) Infineon (WP 1, 3, 4 and 6) aims to conduct R&D concerning both frontend and backend-related technologies. This includes the following work packages on frontend: sensor technology for radar applications (SiGe/Si-semiconductor technology), sensor technology for automotive applications based on magneto-resistive principles, sensor technology for mobile communication and Internet of Things. The work packages on backend will comprise of Fan-out Wafer Level Package technology (eWLB) for new applications in the field of sensors and flexible FID line for pressure and magnetic sensors.

- Bosch (WP 1, 2, 4 and 6) targets to research and develop highly (f) innovative MEMS technology and smart sensors in cooperation with European partners within and beyond IPCEI Microelectronics. The focus hereby will be on applications in the automotive as well as the consumer domain. The RDI will address inertial and pressure sensors for consumer and automotive applications, as well as an optical micro mirror system for display. The particular challenge for the research and development of these devices is the further development of the MEMS element that needs to be strongly redesigned to reach the targeted high performances. Furthermore several innovations will be introduced through capacitive sensing and advanced packaging technologies. Another highlight is a new circuit concept for the evaluation electronics, which is trimmed for particularly low power consumption. These will result in innovative solutions, especially for new fields of application such as virtual reality (VR), AR, civil drones and indoor navigation. Unique semiconductor FID infrastructure and FID-equipment will be developed and implemented for 300 mm wafers as well as 200 mm wafers, setting new standards for automation. The goal is to introduce "digital factory" and Industry 4.0 principles as well as enforcing a flexible, adaptive and sustainable facility, in order to investigate the synergy and feasibility of combining, for the first time, mixed signal, power discrete processes and MEMS processes.

(g) ST-France (WP 1, 3, 5 and 6)

Innovative CIS, [...]

Time-of-Flight based innovative products, [...]

Enabling Technologies involving various bonding and multilayer approaches, and allowing new applications such as micro displays or optical free space communication

Innovative Integrated Vision Systems, involving inclusion of dedicated IPs

(h) ST-Italy (WP 2, 4, 5 and 6)

Work packages Frontend:

MEMS micro-actuators and intelligent devices technologies [...] for new MEMS in emerging applications

FID line enhancement for MEMS and smart sensors

AMR Magnetometer for E-compass applications (Location based services), Movement and Position detection as well as Magnetic field measurements (Magnetic Signature)

Work packages Backend:

New packing solutions to integrate the ASIC die & the MEMS sensors in a System in Package 3D configuration [...]

- (i) TDK-Micronas (WP 3 and 6) aims to establish the next-generation of magnetic-field sensors within the IPCEI Microelectronics project. The well-known Hall Effect will be further utilized as the core technology for measuring the magnetic field through the introduction of a series of innovations to make such sensors much more sensitive, robust and integrated. This serves as an intermediate for many types of position sensing (linear, angle and 3D) in all kinds of application (e.g. Automotive, Consumer, Industrial). These new devices will set new standards with regards to performance and quality, as they will be more sensitive to the target and much more robust against disturbances like mechanical stress or external magnetic fields (e.g. EMC effects).

- (j) ULIS (WP 1, 4 and 6) proposes to develop innovative thermal systems for emerging markets and applications where the thermal sensing will bring a clear added value in terms of performances, robustness and reliability. [...]. The ULIS project aims at developing a new range of technologies to enable the design and the manufacturing of new advanced thermal imagers dedicated to the Mobility, especially Automotive and IoT markets. [...].

- (k) X-FAB FR (WP 4 and 6) will develop an innovative open-access analogue mixed-signal technology platform suitable for the manufacturing of sensor ICs targeting multiple areas like automotive, industry, medical, IoT, and

others. The activities are mainly focused on integration of various functionalities like embedded automotive-qualified non-volatile memory, special optical sensing capabilities, etc. leading to a unique technology portfolio in Europe.

- (I) X-FAB DE (WP 2, 4, 5 and 6) will focus on the development of nextgeneration MEMS-sensor technologies and special technologies for heterogeneous integration like micro-transfer printing to enable a new area of More-than-Moore technologies. New pressure and temperature sensor systems will be enabled by new wafer-level bonding technologies and special piezoelectric material integration and the capabilities of processing these sensor systems. The goal is to offer the necessary technology and standardized fully qualified open-access process blocks to serve different applications and to reduce time-to-market for end users. This will be supported by new to be established FID infrastructure which will apply Industry-4.0 concepts and will allow for new approaches regarding logistics and manufacturing execution.

- (63) The Member States submit that without the public funding provided within the framework of the IPCEI Microelectronics, R&D&I as well as R&D in FID efforts done by the relevant industry in the field of smart and secure sensor systems would be significantly lower in the European Union. Technological innovation as well as novel contributions to the value chain would not develop in the EU. This would not only lead to lower technological competences of the participating partners. More importantly,

- the highly expected reduction of the carbon footprint from advanced systems would not take place to the same extent,

- the further development of the Industry 4.0 would be hindered,

- the further reduction of traffic fatalities would be slowed down, related to slower progress in automated driving.

- leading European OEMs of [...] systems for [...] and other applications will have to integrate sensors from suppliers who pose increased risk of [...] with respect to [...].

- devices used in [...] and in [...] could be supplied by [...] fabs only to a lesser extent. [...] of the partners would be put into question.

- Increase of technical know-how by spillover effects by IPCEI Microelectronics would be stalled,

- Smart sensor networks will lay the technological base for new digital business models, since they serve as interface/link between the real world and its digital representation. Smart sensor may drive economy and society, on the precondition of leading edge sensor technology from the participating.

## 2.2.4. Advanced optical equipment (Technology Field 4, TF4)

(64) The Member States claim that the overarching objective of TF4 is to strengthen R&D&I for Europe's semiconductor equipment industry with specific focus on Extreme Ultra Violet (EUV) technology, which is currently developed for introduction in the semiconductor factories for future high-end chip manufacturing in the next decade. To secure incessantly technical progress in Europe, several technological challenges have to be met. Two of them will be addressed in TF4: the development of a EUV optics with sub-10nm resolution potential and the development of corresponding EUV masks, both in a performance meeting the requirements of future IC volume production. The EUV optical system to be developed is based on a new and totally disruptive technical approach never used for semiconductor manufacturing before. The same holds true for the EUV mask. Therefore the availability of both techniques might revolutionize the manufacturing process of integrated components and devices in future since it might allow improving the resolution of the patterning process of integrated circuits [...]. Fully exploring this resolution potential would allow decreasing the chip sizes of semiconductor integrated circuits [...]. Resulting from first R&D achievements, FID for the EUV optics systems and the EUV masks will be realised.

- (65) In addition, the TF4 partners will develop Advanced Methods for Chip Manufacturing Enhancement and will make them available for all interested companies. This technique is still not in use at European semiconductor companies.

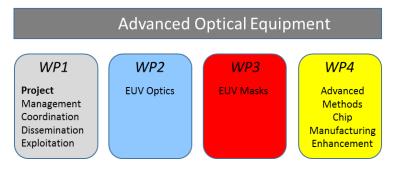

- (66) The Member States submit that the work in TF4 will be organised in the following work packages, with contribution of the partners as described below:

Figure 5: work packages in TF4

- (67) **WP1 Management.** (Lead Partner Zeiss) In this work package the development activities between the TF4 partners, and the collaboration with the associated partners will be coordinated. It supports the project leader for the timely supply of the project documents and the project reporting on technical results. It further organizes the exchange of results within the project, and the contributions to workshops and conferences for public dissemination. In addition, project engineering will be organized, specifically in case of deviations from work plans or adaption to a changing technical environment. Coordination towards the overall IPCEI Microelectronics project leader and governance organization will be done.

- (68) **WP2 EUV Optics.** (Lead Partner Zeiss): Development of a high resolution Hyper NA EUV optics system and corresponding manufacturing equipment for an optics factory

For high performing EUV optical system manufacturing about [...] tools and instruments need to be developed and installed in the optics factory, the majority of them will have to be tailored to the specific requirements for manufacturing of Hyper NA EUV projection systems. R&D&I activities will comprise in-house development and manufacturing of tools and instruments, enablement and

guidance of external suppliers, as well as activities needed for integrating the tools in the line and their technological process qualification. A variety of new unit manufacturing processes will be developed; most of them will by far exceed state-of-the-art technical manufacturing limits. At the end of the IPCEI Microelectronics project a line for fabrication of the optics components, modules and sub-systems and for their integration to the optical system will be available. All R&D&I activities will be based on preceding results for the Hyper NA EUV optics design, optics construction and integration concepts as well as advanced optics metrology concepts for both, the EUV projection objective and EUV illumination system.

(69) **WP3** – **EUV Masks.** (Lead Partner AMTC) Development of a EUV mask manufacturing technology and first industrial deployment of a EUV mask manufacturing line.

A number of advanced tools will be implemented into the line, qualified and the associated unit processes developed to setup an integrated EUV mask line. These new tools address the critical unit processes of the mask manufacturing process and will enable with their advanced technology development of unit processes to achieve requirements of the Key Performance Indicators (KPI) of a EUV Mask.

The integration of a Multi-Ebeam-Writer as a complete new disruptive technology into the mask manufacturing process is pursued to enable required KPI on pattern placement and feature fidelity.

New etch tools will improve the uniformity of the features across the mask. High end inspection/repair tools will enable AMTC to find critical defects and improve mask defectivity to a level appropriate for a HVM chip manufacturing. R&D&I activities comprise the integration of the processes and their optimization to enable the needed mask quality capability. This includes also the determination of process limitations and the setup of procedures for process control. The development of a final mask manufacturing process requires deep understanding of the unit processes with the related evaluation and development steps and their interplay in an integrated environment.

In collaboration with AMTC, Zeiss will support the development of repair techniques for EUV masks, which can comprise chip layouts adapted to the Hyper NA imaging requirements. Such EUV masks will be indispensable for the success of future miniaturization of electronic devices based on EUV technologies.

## (70) WP4 – Advanced Methods for Chip Manufacturing Enhancement (AMCME)