## **Open, Secure, Extreme Edge AI for the IoT**

An Open Source Hardware Success Story

14.11.2019

<sup>1</sup>Department of Electrical, Electronic and Information Engineering

> **ETH**zürich <sup>2</sup>Integrated Systems Laboratory

Luca Benini<sup>1,2</sup>

CONDS NATIONAL SUISSE Schweizerischer Nationalfonds Sondo nazionale svizzero Swiss National Science Foundation

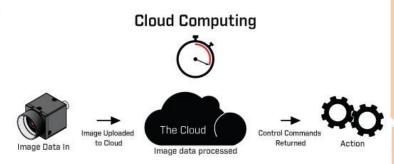

#### Idea in 2013: Cloud $\rightarrow$ Edge $\rightarrow$ Extreme Edge Al

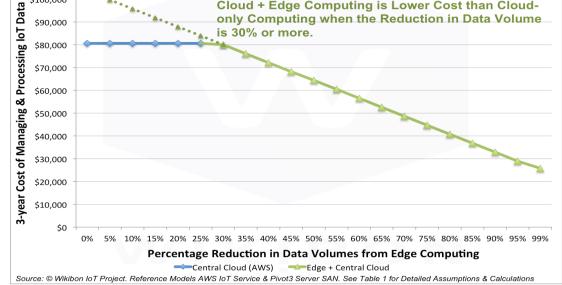

#### Total Cost of Remote IoT Processing as a Function of Data Reduction at the Edge (200 Miles Distance)

#### #1 Customer Question on Amazon.com (out of 1,000+):

I don't want any of my (private, personal) videos on any servers not in my control. Is this possible?

#2 Customer Question on Amazon.com (out of 1,000+):

2. How long does the battery charge last?

ource: www.amazon.com/ask/guestions/asin/B01M3VHG87/

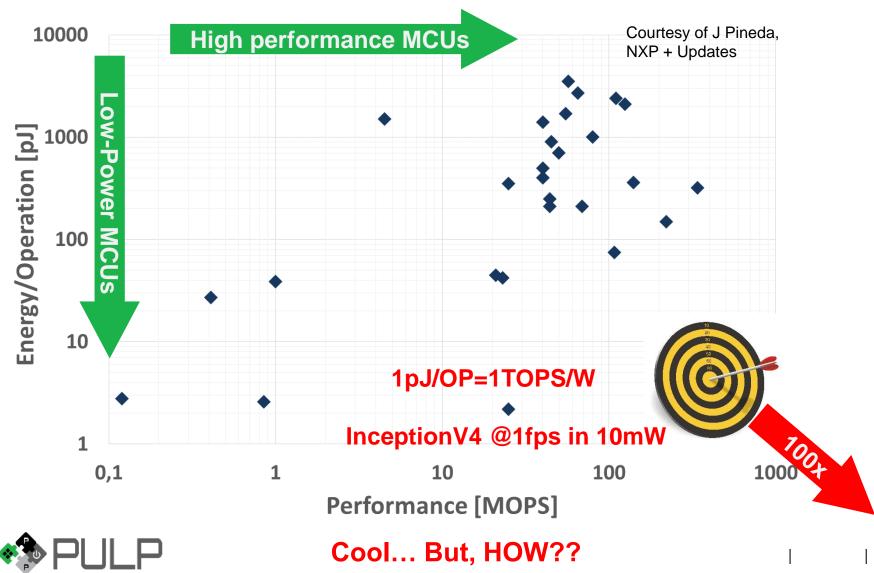

Extreme edge (i.e. on sensor) Al challenge Al capabilities in the power envelope of an MCU: 100mW and below

## **Energy efficiency is THE Challenge**

Current AI models need GOPS - Edge devices have mW power budget

#### Need a low power MCU that is good at AI $\rightarrow$ Bespoke ISA!

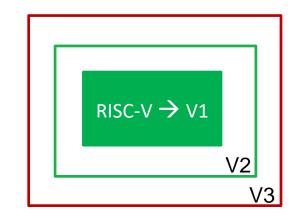

A modern, open, free ISA, extensible by construction! Endorsed and Supported by 130+ Companies

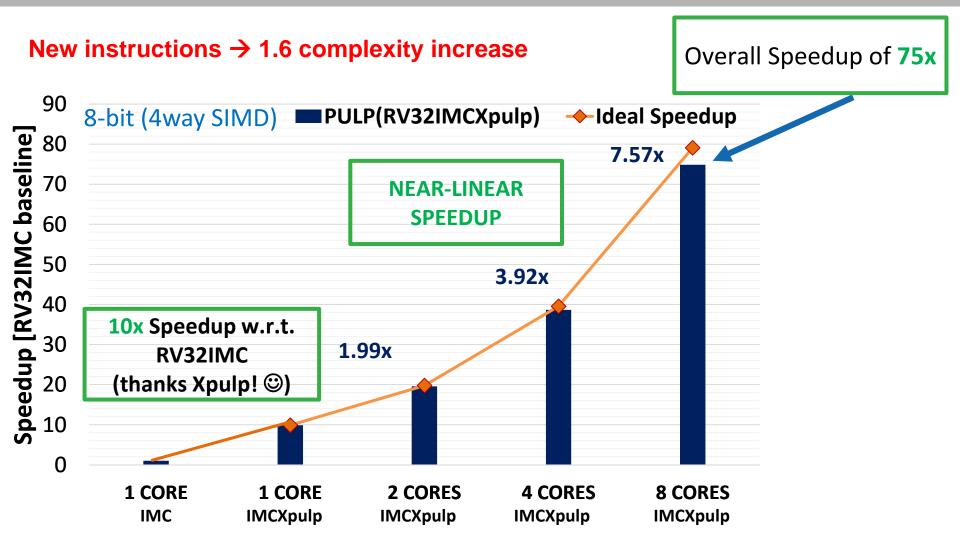

- V1 Baseline RISC-V RV32IMC HW loops

- V2 Post modified Load/Store Mac

- V3 SIMD 2/4 + DotProduct + Shuffling Bit manipulation unit Lightweight fixed point

But... Low Energy comes from ISA+architecture+implementation

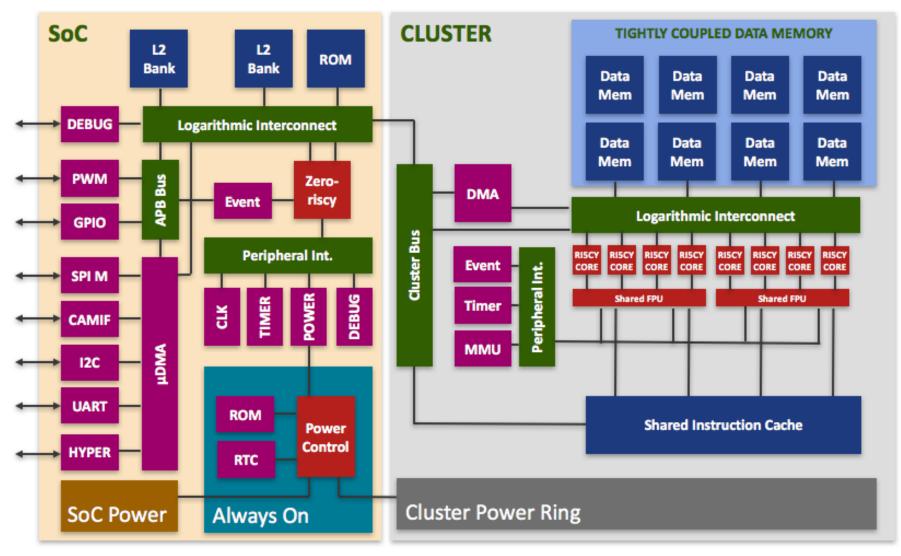

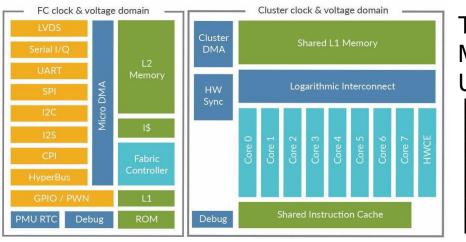

#### PULP: Ultra-Efficient Open (multi)-processor design based on Open ISA

M. Gautschi et al., "Near-Threshold RISC-V Core With DSP Extensions for Scalable IoT Endpoint Devices," in IEEE TVLSI, Oct. 2017.

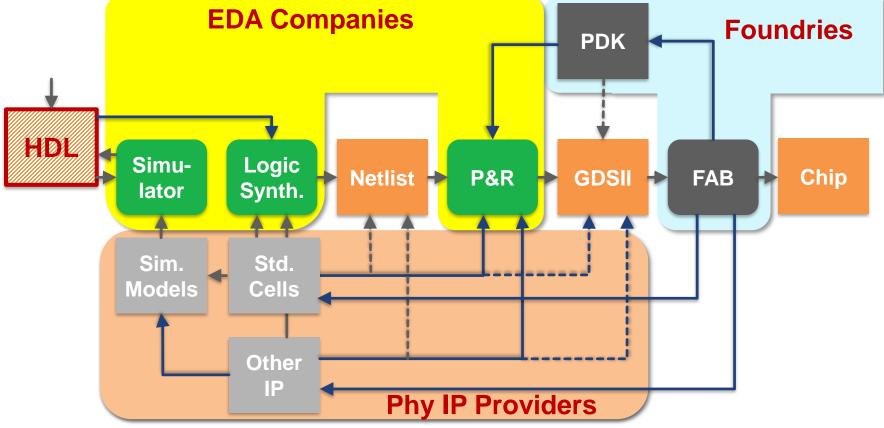

#### Nice, but what exactly is "open" in Open HW?

- Only the first stage of the silicon production pipeline can be open HW

→ RTL source code (in an HDL such as SystemVerilog)

- Later stages contain closed IP of various actors + tool licensing issues

Permissive, Copyright (e.g APACHE) License is Key for industrial adoption

#### Again Nice, but... Why Open Source HW?

- For science ... fundamental "research infrastructure"

- Community building: sharing of ideas, artefacts

- Fantastic tool for dissemination (more citations <sup>©</sup>)!

- Reduce "getting up to speed" overhead for partners

- Enables fair and well controlled benchmarking

- For Business ... it is truly disruptive

- Reduces the NRE cost for silicon design

- Faster innovation path for startups

- New business models (for profit and non-for profit)

- Helps exchange of information across NDA walls

- Great for Marketing & Training

- For society ...long term sustained benefits

- More innovation, growth, jobs

- Personalized silicon vision "Moore-for-all"

- More Secure, safe, auditable HW

**DARPA Posh Open Source Hardware (***POSH***):** An open source System on Chip (SoC) design and verification ecosystem that enables cost effective design of ultra-complex SoCs

USA's electronics resurgence intitiative

### Results: RV32IMCXpulp vs RV32IMC

#### The Core is not enough $\rightarrow$ Open IoT Processor

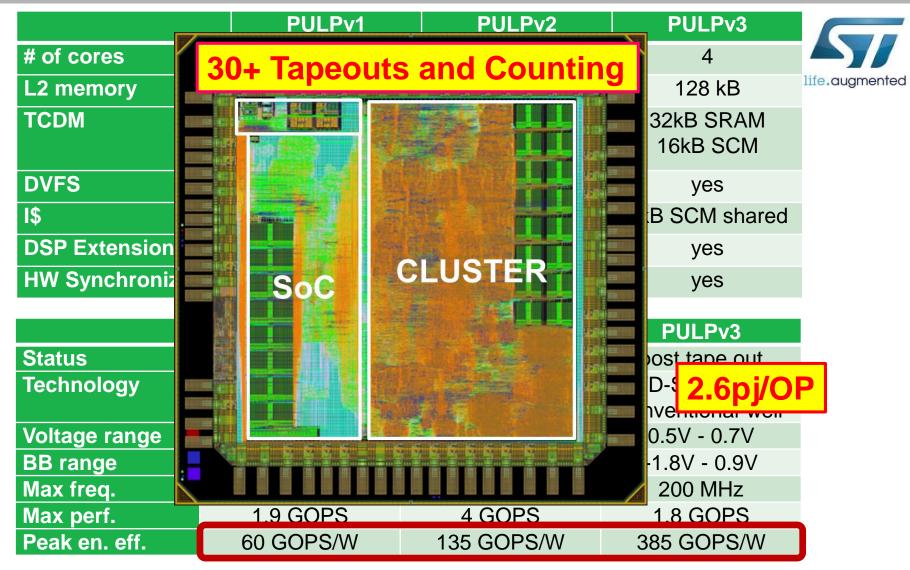

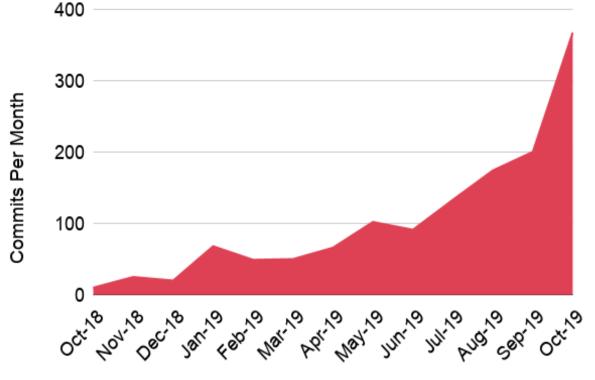

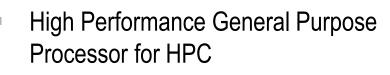

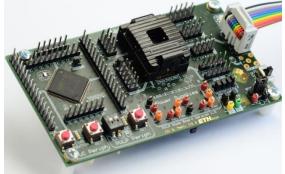

### Simulation is not enough $\rightarrow$ Silicon Proven Open HW

### Prototype is not Enough $\rightarrow$ Open HW-based SoC Product

- Best in class

Instruction Set

Architecture (ISA)

- GWT Member of RiscV Foundation

- Open Source Computing Platform created by ETHZ and UniBo

- Permissive license (solderpad)

- Multiple tape outs

- GWT contributes to PULP

## GREENWAVES

- Innovating on Risc-V and PULP

- GAP8: Proprietary balanced system solution (SOC) based on PULP open source elements plus GWT proprietary elements both on HW and SW/Tools side

#### GAP8 is in mass production now

TSMC 55LP 1.0V to 1.2V Max f: 133-250 MHz Up to 12.8 GOPS (8bit)

| 新建 |  |

|----|--|

| e. |  |

|    |  |

|    |  |

|    |  |

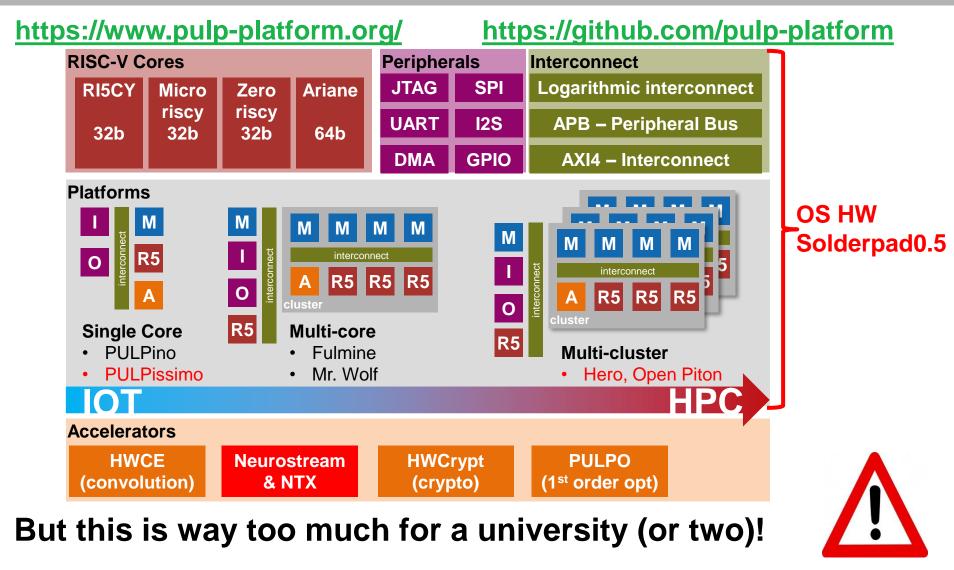

### Putting it all together: The Open PULP platform

#### Academic Open-Source $\rightarrow$ Industrial Open source

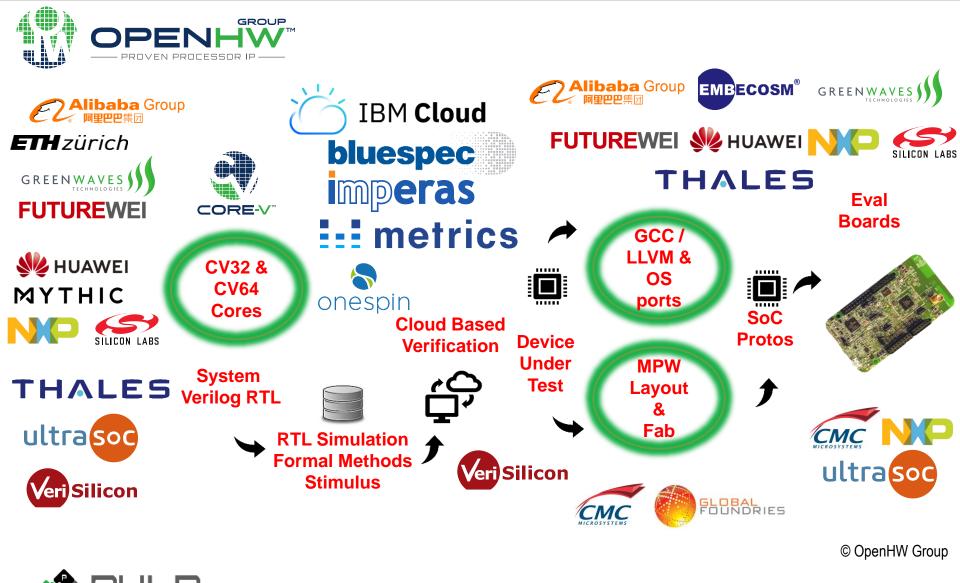

Rick O'Connor (OpenHW CEO, former RISC-V foundation director)

- OpenHW Group is a not-for-profit, global organization (EU,NA,Asia) driven by its members and individual contributors where HW and SW designers collaborate in the development of open-source cores, related IP, tools and SW such as the CORE-V Family of cores.

- OpenHW Group provides an infrastructure for hosting high quality opensource HW developments in line with industry best practices.

#### **OpenHW Group Ecosystem**

#### A Vertical, Application-focused Open-Platform Approach

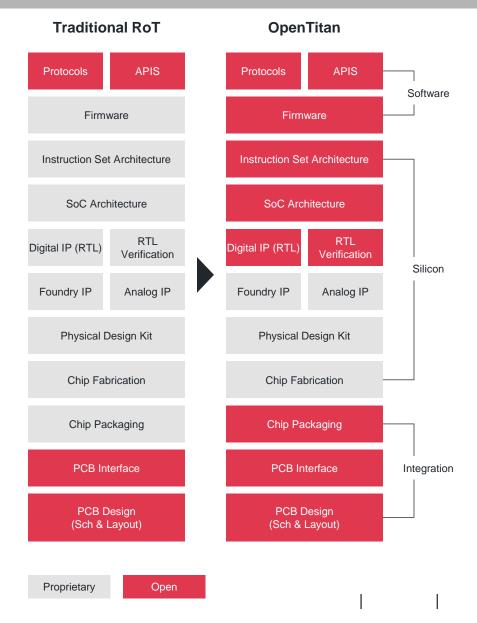

#### **Open**Titan

More transparent, trustworthy, and secure RoT chip design

OpenTitan is the first open source silicon project building a transparent, high-quality reference design for silicon root of trust (RoT) chips.

# 🛟 opentitan

#### **Founding partners**

| <b>ETH</b> zürich | G+D<br>Mobile Security |

|-------------------|------------------------|

|                   |                        |

Google nuvoton Western Digital.

## **Open HW enables a New Level of Openness in Security**

#### Transparent: Open implementation

- Transparency at the bottom; lower than any existing RoT solutions

- Transparency enables the community to proactively audit, evaluate, & improve the design

- Engineering: reference firmware, register-transfer level (RTL), design verification (DV), and integration guidelines

#### Feel the momentum!

Ibex RISC-V core, flash interface, communications ports, cryptography accelerators, and more.

### NoT only IoT: the European Processor Initiative

SURF SARA

**SKIT**

Rolls-Royce

#### **Europe Needs its own Processors**

- Processors now control almost every aspect of our lives

- Security (back doors etc.)

- Possible future restrictions on exports to EU due to increasing protectionism

- A competitive EU supply chain for HPC technologies will create jobs and growth in Europe

- Sovereignty (data, economical, embargo)

**ETH** zürich

Atos

LISBOA

UNIVERSITÀ DI PISA

GENCI

PROVe & PLI

Cinfineon

COMPUTER

BSC

Elektrobit

🗾 Fraunhofer

cea

TOLI

menta

- High-performance RISC-V based accelerator

- Computing platform for autonomous cars

- Will also target the AI, Big Data and other markets in order to be economically sustainable

#### www.pulp-platform.org

The fun is just beginning...